[FPGA] Vivado で ZedBoard 用のプロジェクトを作成

準備

電源と電源の隣に PROG と書かれた USB があるので、そこに接続する。FPGA にコンフィグ(書き込む)場合は、PROG への接続が必要。また、FPGA から出力をする場合は、UART と書かれた USB にも接続が必要。USB ケーブルは2本使う。

プロジェクト作成

Vivado 起動後の画面で、Create Project からプロジェクトを作成。

Project name に任意のプロジェクト名を指定し、次の画面では「RTL Project」を選択して、この時「Do not specity sources at this time」にチェックをいれておく。

ターゲットとなるボードを選択できるので、Search に ZedBoard と入力して、表示された「ZedBoard Zynq Evaluation and Development Kit」を選択。もし、表示されなければ「Refresh」を押せば更新されるかも。

この後に「Finish」を押せばプロジェクトが作られる。

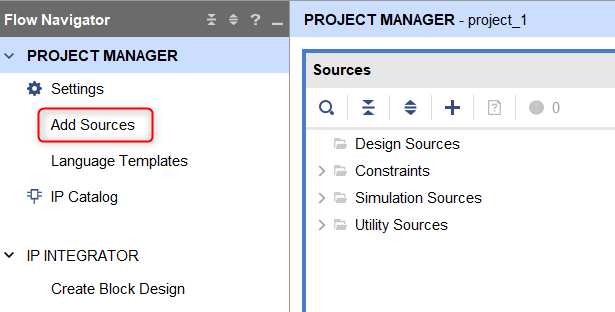

ファイルの追加

Flow Navigator の Add Sources を選択すると追加用のダイアログが開くので、「constraints」と「design sources」をそれぞれ選択して追加していく。

「Add Files」から、それぞれ .xdc (constraints) や .v (design sources) などを追加していく。この時「Copy Sources into project」のチェックは off。「Scan and add RTL include files into project」のチェックは on にしておく。

Bitstream の生成

Design Sources と Constraints を追加したら Bitstream を生成する。左側のパネルの「PROGRAM AND DEBUG」から「Generate Bitstrea」を押す。

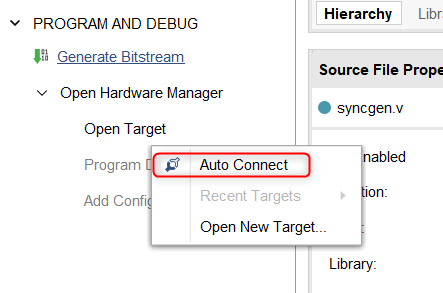

FPGA に書き込む

FPGA を PC に接続して電源を入れる。「PROGRAM AND DEBUG」の Open Hardware Manager -> Auto Connect を選択する。上部に「Program Device」が出てくるので、選択すると書き込める。

Reference

FPGA プログラミング大全 Xilinx 編