[FPGA] Zedboard (Zynq) の開発環境 Vivado の導入

ダウンロード

Zynq の開発には Vivado と Vitis を導入する。

ハードウェア開発には Vivado を使用し、ソフトウェア開発には Vitis が使用できる。どちらも Xlinx 統合インストーラからインストールが可能になっている。なお、ダウンロードにはユーザー登録が必要。

Xlinx のダウンロードページ

https://japan.xilinx.com/support/download/index.html/content/xilinx/ja/downloadNav/vivado-design-tools.html

インストール

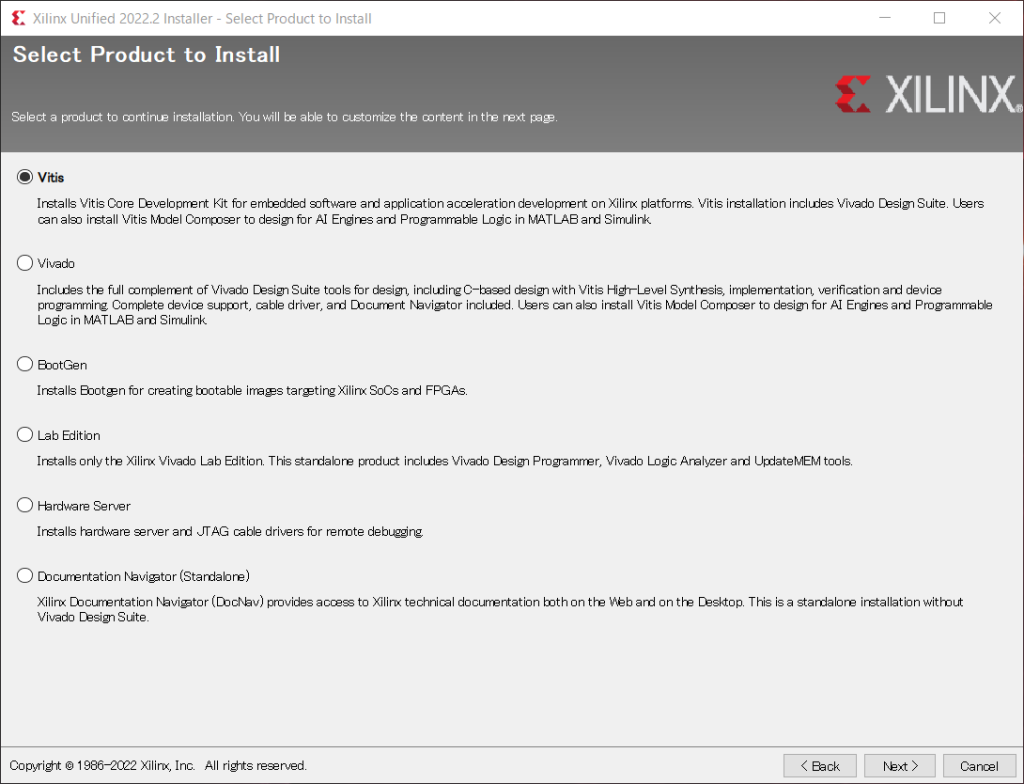

インストール時に Vitis を選択すれば、Vivado と Vitis の両方がインストールされる。(Vivado を選択した場合は Vitis が入らないので注意)他の項目は全てデフォルトのチェックのままにした。

ドキュメント

Constrains

Vivado Design Suite ユーザー ガイ ド 制約の使用

https://www.xilinx.com/content/dam/xilinx/support/documents/sw_manuals_j/xilinx2021_2/ug903-vivado-using-constraints.pdf

set_property PACKAGE_PIN L16 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

create_clock -period 8.000 -name sys_clk_pin -waveform {0.000 4.000} -add [get_ports clk]-period 8.0 -waveform {0.000 4.000}

周期の長さが 8ns で 4ns ごとの繰り返し。(125MHz)

set_property PACKAGE_PIN Y9 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

create_clock -period 10.000 -name sys_clk_pin -waveform {0.000 5.000} -add [get_ports clk]-period 10.000 -waveform {0.000 5.000}

周期の長さが 10ns で 5ns ごとの繰り返し。(100MHz)

-period, -wveform の定義については、上記ドキュメントを参考。-name sys_clik_pin はクロック名を定義。

Zedboard のピン

Zedboard の Constrains は Digilent の Github に上がっているファイルを参考。

https://github.com/Digilent/digilent-xdc/blob/master/Zedboard-Master.xdc

例えば、クロックは Y9 だった。

set_property -dict { PACKAGE_PIN Y9 IOSTANDARD LVCMOS33 } [get_ports { clk }];

create_clock -period 10.000 -name sys_clk_pin -waveform {0.000 5.000} -add [get_ports clk]

set_property -dict { PACKAGE_PIN P16 IOSTANDARD LVCMOS18 } [get_ports { reset }];

set_property -dict { PACKAGE_PIN AA19 IOSTANDARD LVCMOS33 } [get_ports { vga_hs }];

set_property -dict { PACKAGE_PIN Y19 IOSTANDARD LVCMOS33 } [get_ports { vga_vs }];

set_property -dict { PACKAGE_PIN Y21 IOSTANDARD LVCMOS33 } [get_ports { vga_b[1] }];

set_property -dict { PACKAGE_PIN Y20 IOSTANDARD LVCMOS33 } [get_ports { vga_b[2] }];

set_property -dict { PACKAGE_PIN AB20 IOSTANDARD LVCMOS33 } [get_ports { vga_b[3] }];

set_property -dict { PACKAGE_PIN AB19 IOSTANDARD LVCMOS33 } [get_ports { vga_b[4] }];

set_property -dict { PACKAGE_PIN AB22 IOSTANDARD LVCMOS33 } [get_ports { vga_g[1] }];

set_property -dict { PACKAGE_PIN AA22 IOSTANDARD LVCMOS33 } [get_ports { vga_g[2] }];

set_property -dict { PACKAGE_PIN AB21 IOSTANDARD LVCMOS33 } [get_ports { vga_g[3] }];

set_property -dict { PACKAGE_PIN AA21 IOSTANDARD LVCMOS33 } [get_ports { vga_g[4] }];

set_property -dict { PACKAGE_PIN V20 IOSTANDARD LVCMOS33 } [get_ports { vga_r[1] }];

set_property -dict { PACKAGE_PIN U20 IOSTANDARD LVCMOS33 } [get_ports { vga_r[2] }];

set_property -dict { PACKAGE_PIN V19 IOSTANDARD LVCMOS33 } [get_ports { vga_r[3] }];

set_property -dict { PACKAGE_PIN V18 IOSTANDARD LVCMOS33 } [get_ports { vga_r[4] }];定義メモ

参考

FPGA マガジン No.7